### MEng Individual Project Report

# HIGH PERFORMANCE PARALLEL DESIGN BASED ON SESSION PROGRAMMING

Nicholas Ng (cn06@doc.ic.ac.uk)

Department of Computing

Imperial College London

Supervisor

Nobuko Yoshida (yoshida@doc.ic.ac.uk)

Second Marker Wayne Luk (wl@doc.ic.ac.uk)

## **Contents**

| 1 | Intr | oduction                             | 11 |

|---|------|--------------------------------------|----|

|   | 1.1  | This project                         | 13 |

|   | 1.2  | Contributions                        | 13 |

| 2 | Bacl | kground                              | 15 |

|   | 2.1  | Pi-calculus                          | 15 |

|   |      | 2.1.1 Asynchronous $\pi$ -calculus   | 15 |

|   | 2.2  | Session types                        | 17 |

|   |      | 2.2.1 Syntax of session calculus     | 17 |

|   | 2.3  | Multiparty session types             | 19 |

|   | 2.4  | Session programming with SJ          | 20 |

|   |      | 2.4.1 Branching                      | 22 |

|   |      | 2.4.2 Iteration                      | 23 |

|   |      | 2.4.3 Delegation                     | 24 |

|   |      | 2.4.4 Non session-based alternatives | 24 |

|   |      | 2.4.5 Related work                   | 25 |

|   | 2.5  | Axel                                 | 25 |

|   |      | 2.5.1 Hardware arrangement           | 25 |

|   |      | 2.5.2 Software                       | 26 |

|   |      | 2.5.3 Performance                    | 28 |

|   | 2.6  | Parallel Algorithms                  | 28 |

|   |      | 2.6.1 N-body simulation              | 28 |

|   | 2.7  | Summary                              | 30 |

| 3 | Desi | gn and Implementation                | 31 |

|   |      | Design goals                         | 31 |

4 CONTENTS

|   | 3.2   | Session.    | Java on Axel                            | 32  |

|---|-------|-------------|-----------------------------------------|-----|

|   |       | 3.2.1       | Overall design                          | 32  |

|   |       | 3.2.2       | Application topology and session typing | 34  |

|   | 3.3   | SJ with l   | FPGA                                    | 36  |

|   |       | 3.3.1       | The need for cross-language features    | 36  |

|   |       | 3.3.2       | Java Native Interface                   | 37  |

|   |       | 3.3.3       | Java Native Access                      | 37  |

|   |       | 3.3.4       | Problems encountered                    | 38  |

|   | 3.4   | C-transla   | ation of SJ n-body implementation       | 39  |

|   |       | 3.4.1       | Why would this work?                    | 40  |

|   |       | 3.4.2       | A SJ primitives library for C           | 40  |

|   |       | 3.4.3       | Shortcomings of the library             | 42  |

|   | 3.5   | Summar      | у                                       | 42  |

| 4 | Corı  | rectness I  | Proof of N-body Implementation          | 43  |

|   | 4.1   | Session     | calculus with multichannel in/outwhile  | 43  |

|   | 4.2   | Syntax .    |                                         | 44  |

|   | 4.3   | Operatio    | onal semantics                          | 44  |

|   | 4.4   | Type sys    | tem                                     | 46  |

|   |       | 4.4.1       | Duality                                 | 47  |

|   |       | 4.4.2       | Typing environment                      | 48  |

|   |       | 4.4.3       | Typing rules                            | 48  |

|   | 4.5   | Subject 1   | reduction                               | 52  |

|   |       | 4.5.1       | Well-formed topology                    | 53  |

|   |       | 4.5.2       | Subject congruence theorem              | 54  |

|   |       | 4.5.3       | Subject reduction theorem               | 56  |

|   | 4.6   | Progress    | property                                | 60  |

|   | 4.7   | Correctn    | ess proof for n-body simulation         | 61  |

|   |       | 4.7.1       | N-body simulation in session calculus   | 61  |

|   | 4.8   | Summar      | y                                       | 62  |

| 5 | Testi | ing and F   | Evaluation                              | 63  |

| - | 5.1   | _           | ive designs                             | 63  |

|   |       |             | SJ and acceleration hardware allocation | 63  |

|   |       |             | Communication medium                    | 64  |

|   |       | - · · · · · |                                         | J 1 |

|    | 5.2    | Pre-im  | plementation tests: inner product             | 65        |

|----|--------|---------|-----------------------------------------------|-----------|

|    |        | 5.2.1   | JNA direct mapping                            | 65        |

|    |        | 5.2.2   | JNA interface mapping and direct mapping      | 66        |

|    |        | 5.2.3   | Execution in CPU and FPGA                     | 66        |

|    | 5.3    | Bench   | marks                                         | 68        |

|    |        | 5.3.1   | Benchmark methodology                         | 69        |

|    |        | 5.3.2   | Benchmark results                             | 69        |

|    |        | 5.3.3   | Comparing with Axel's implementation          | 73        |

|    |        | 5.3.4   | Benchmark results conclusion                  | 73        |

|    | 5.4    | Summ    | ary                                           | 74        |

| 6  | Con    | clusion |                                               | 75        |

|    | 6.1    | Future  | work                                          | 76        |

| A  | App    | endix   |                                               | <b>79</b> |

|    | A.1    | Java N  | lative Interface (JNI) example                | 79        |

|    | A.2    | Java N  | Tative Access (JNA) example                   | 80        |

|    | A.3    | Compa   | arison of SJ and C-translation implementation | 82        |

|    | A.4    | SJ + F  | PGA speedup over SJ implementation            | 85        |

| Bi | bliogr | aphy    |                                               | 78        |

6 CONTENTS

#### **Abstract**

Session programming is a programming model based on the theory of session types, a typing system for  $\pi$ -calculus. Session types is developed to model structured interaction between processes and correctly typed process will have the property of communication safety. Session Java (SJ) is a full implementation of session types in Java. In this project, We aim to introduce the session programming model to Axel, a heterogeneous cluster with both FPGAs and GPUs as hardware accelerators to design communication safe parallel algorithms.

We give an implementation of a parallel algorithm, n-body simulation, on the Axel cluster, using SJ and FPGAs. We also give a translation of our SJ n-body simulation into C to get a higher performance. We find good performance improvements in both implementations, without compromising safety property of our program.

Finally, we present a formalisation of two new *multichannel* SJ primitives for parallel programming. We use the formalisation to prove the correctness of our n-body implementation and generalise the proof to a ring topology used by parallel algorithms in SJ.

8 CONTENTS

## Acknowledgements

I would like to thank the following people, without whom this project might not be as successful. My supervisor, Dr. Nobuko Yoshida for her enthusiasm and guidance throughout the project, my second marker, Prof. Wayne Luk for his constructive advices and feedback on the project, Andi Bejleri for the crash course on session types, Brittle Tsoi for his help on FPGA and the Axel cluster, Olivier Pernet for his insights and advices to the direction of the project, Raymond Hu for advices and support on SJ, Wilhelm Kleiminger for moep and proofreading my final report, and finally, my family for their support and love throughout my four years at university.

10 CONTENTS

## Chapter 1

## Introduction

In 1965, Gordon Moore predicted that the number of transistors on a chip doubles about every two years [?]. 45 years later, Moore's Law remained valid and is generalised to describe the performance growth of microprocessors. Until recent years, microprocessor manufacturers have enjoyed performance increase simply by cramming more transistors on a single microprocessor. As the cost of performance rose to an unfeasible level due to power consumption, to keep up with Moore's Law, research and development on computer architecture turned towards parallelising techniques on existing hardware. Multicore processor architecture rose in popularity, today it is easy to find dual-, quad-, even hexa-cores on a single processor dice, and we are expecting to see processors with as much as 80-cores in the next few years [?].

On a much bigger scale, another type of parallel architecture is *computer clusters*. It is a form of distributed computing, where multiple standalone cluster nodes are connected and computation jobs are shared between the nodes. Each node can work on their partition of jobs in parallel. From outside the cluster, the jobs submitted to the cluster are completed as if a single computer is used. As a cluster can be built using commodity hardware, it is a cost-effective way of building supercomputers.

Parallel models of computing has shown it self as a promising direction to higher performance computer architecture.

Another trend that saw a lot of interest lately is the use of *hybrid architectures* to achieve high performance. Instead of using a centralised computation model based on the CPU, parts of computations are delegated to other specially designed hardware which can perform the computation more efficiently.

Field Programmable Gate Array (FPGA) is a type of reconfigurable integrated circuit. FP-GAs can be configured to represent software instructions directly in hardware during runtime. On CPUs, all instructions need to go through the fetch-decode-execute cycle before they can be executed. Implementations in FPGAs do not require the fetch-decode phase since the instructions are already represented in the hardware circuit. As a result, FPGAs are much more efficient than CPUs in computation-heavy tasks. Also because the computations are done in hardware circuit, pipelined instructions can be executed in parallel as a physical property of electric circuits.

A modern GPU can double as a many-core general purpose processor. A GPU has hundreds of processing cores which are very capable at floating point computation, as they are usually used for graphics calculations. *Common Unified Device Architecture* (CUDA) and ATI's *Stream* are software frameworks that allow the use of the GPU cores for non-graphical computations. This is known as *General Purpose computation on Graphics Processing Units* (GPGPU). Compared to traditional CPUs where support for *Single Instruction Multiple Data* (SIMD) is limited to the *Streaming SIMD Extensions* (SSE) instruction set which can work on at most four single precision floating point number in parallel, the GPU can work on hundreds of data in parallel in the GPU cores.

The performance edge in parallel architectures do not come without its own problems. Parallel programming is a much less understood model than traditional serial programming model. Some of the problems were solved by the implicit programming model, where programmers do not need to understand parallel programming and parallelisation is done implicitly in hardware or by compiler optimisations. The advantage of this technique is a guarantee of a certain degree of parallelism and the correctness of the parallelised section since most of the optimisations are rather conservative. On the other hand, this approach might not always give the optimal result if a there exists specific ways to parallelise the code as the programmer do not have control over the implicit optimisations. The alternative, explicit parallelism comes typically in form of messagepassing. Often, small trivial mistakes in the program will result in parallel synchronisation issues, race conditions, or deadlocks. Combined with the interleaving of executions, parallel programming in this model cannot guarantee communication safety and is difficult to identify problems as the execution sequence can be undeterministic. For years, computer science theorists seek to understand parallel programming model and search for solutions by formalising and modelling concurrent processes. Amongst the more active researches, the Actor model and process algebras, such as Calculus of Communicating Systems CCS [?] and its successor  $\pi$ -calculus [?, ?], are fields that found most success. With a model of processes interactions, it is much easier to understand the properties of concurrent systems to prevent the issues common in parallel programming.

Session types [?, ?, ?] were developed as a typing system for  $\pi$ -calculus. Interactions between parties are conducted over private channels called sessions. A session type specifies the sequence and typing of interactions in the session. Session types captures the fact that communicating parties must have a compatible typing between them. For example, if a sender intends to send an integer, the receiver must be expecting to receive an integer as well; otherwise there would be problem. By analysing the session typing of communicating processes and making sure only compatible processes can start a session, we are able to show that *communication safety property* holds for session-typed processes - deadlocks are not possible. If a parallel system is modelled in  $\pi$ -calculus is shown to be type-safe by session types, we are confident to say that the system is communication safe.

Session types as a typing system alone cannot be used directly as a design tool. Session Java (SJ) [?] is an implementation of session types as an extension of Java. It is designed to be a non-intrusive addition to Java and integrates well with the object oriented setting. SJ brought the full theoretical session programming framework to a programming language in common use. It is a powerful tool for programmers that can ensure session compatibility within the program-

1.1. THIS PROJECT 13

ming language, without first modelling interactions in the pure theoretical framework, to create communication safe code.

### 1.1 This project

This project aims to explore ways of applying session programming to heterogeneous clusters, which uses acceleration hardware such as FPGAs or GPUs.

We wish to demonstrate uses of session-type based Java to design parallel algorithms which are communication safe, efficient and easily readable on our target platform. We also aim to generalise and extend our approach to other similar platforms so designs on these platforms can also make use of session programming.

#### 1.2 Contributions

In this report we document our findings and results on applying session programming to design parallel algorithms on heterogeneous clusters. We made the following contributions:

- Introduced an architecture for high performance parallel application design with *session Java* (SJ) using heterogeneous hardware (§3.2).

- Implemented a parallel n-body simulation in SJ accelerated by FPGA on a heterogeneous cluster (§3.3), with full sets of benchmark results to compare the performance with and without acceleration hardware (§5.3). Our implementation using SJ and FPGA yields up to 2 times speedup in the best performance.

- Implemented a C library that can be used for session programming in the C programming language (§3.4.2), and a C implementation of n-body simulation translated from SJ to demonstrate the use of the library (§3.4). The translated code has on average 5 times speedup over SJ implementation.

- Presented a formalisation and first correctness proof of a pair of new multichannel SJ primitives inwhile and outwhile in SJ, designed to implement parallel algorithms. (§4.1)

The two primitives can represent parallel topologies more naturally and were shown to be more efficient than its single-channel counterpart.

- Proved our implementation of n-body simulation deadlock free, using the formalisation of the new multichannel SJ primitives (§4.7).

#### **Report organisation**

The report contains six chapters and each chapter is organised as follows:

- Chapter 2: Background will cover the background theories behind session types and session Java. We will also introduce our target platform, a heterogeneous cluster called Axel which contains FPGAs and GPUs as processing elements.

- Chapter 3: Design and Implementation will give the design and implementation details of the main result of the project, an implementation of n-body simulation using SJ and FPGA. We will also include a version of the implementation translated from SJ to C, which is more suitable for deployment on high performance clusters.

- Chapter 4: Correctness proof of n-body implementation will detail an extension to the session type introduced in [?] to include multichannel inwhile and outwhile SJ primitives used for parallel programming in SJ. We will then show a correctness proof of our n-body implementation based on the updated session type.

- Chapter 5: Testing and Evaluation will discuss and evaluate alternative designs and compare benchmark results of different implementations of n-body simulation.

- Chapter 6: Conclusion will conclude our findings of the project and outline potential future works.

## Chapter 2

## **Background**

In this chapter we will discuss fundamental background theories of which session programming is based on. This includes  $\pi$ -calculus (§2.1) - the process calculi which is the modelling basis for session programming, session types (§2.2) - the typing system of  $\pi$ -calculus for sessions-based communication and an introduction to session Java (§2.4) which is the main programming tool we are going to use in the project.

Next, we will introduce the target platform for the project (§2.5) - Axel, a heterogeneous cluster with *Field Programmable Gate Arrays* (FPGAs) and *Graphics Processing Units* (GPUs) as acceleration hardware.

Finally, we will briefly look at the current parallel programming model of Axel and session Java to implement our choice of parallel algorithm - n-body simulation (§2.6).

#### 2.1 Pi-calculus

$\pi$ -calculus [?] is a process calculus proposed by Milner, Parrow and Walker as a successor to *Calculus of Communicating Systems* (CCS) as a model to study concurrent mobile systems. It uses message passing and is distinguished from CCS by its use of names in messages rather that values in CSS. The difference between value passing and name passing is that only name passing allows sending and receiving of *channel names* as messages, so channels can be 'reconfigured' at run time. This makes  $\pi$ -calculus more expressive and suited for mobile processes [?]. There are many variants of  $\pi$ -calculus for different applications, due to the notational differences in different domains.  $\pi$ -calculus and its variants lie a foundation for modelling communication systems, from simple asynchronous  $\pi$ -calculus and spi calculus for session types and cryptography [?] respectively, to more advanced calculi such as  $3\pi$  for developmental and systems biology [?].

#### 2.1.1 Asynchronous $\pi$ -calculus

Asynchronous  $\pi$ -calculus is the simplest variant of  $\pi$ -calculus and is the variant which session type (§2.2) is based on.

| processes                                                           | P,Q ::=                |

|---------------------------------------------------------------------|------------------------|

| nil process                                                         | 0                      |

| parallel composition of P and Q                                     | $P \mid Q$             |

| generation of a with scope P                                        | (va)P                  |

| replication of P                                                    | !P                     |

| output of v on channel u                                            | $ar{u}\langle v angle$ |

| input of <i>distinct</i> variables $x$ on $u$ , with continuation P | u(x).P                 |

Fig. 2.1: Syntax of asynchronous  $\pi$ -calculus

#### **Syntax**

The main difference between full  $\pi$ -calculus and asynchronous  $\pi$ -calculus is asynchronicity. This means after an output action, there is no continuation and the process terminates when the message is delivered. Communication with asynchronous  $\pi$ -calculus is therefore deadlock free. Asynchronous communication can be used to simulate synchronous communication, and is common in distributed systems. Fig. 2.1 shows the syntax of asynchronous  $\pi$ -calculus.

#### **Reduction rules**

$$\bar{a}\langle v \rangle \mid a(x).P \to P\{^v/_x\}$$

[COM]

$$\frac{P \to P'}{P \mid Q \to P' \mid Q}$$

[PAR]

$$\frac{P \to P'}{(va)P \to (va)P'}$$

[RES]

$$\underline{P \equiv Q \to Q' \equiv P'}$$

[STRUCT]

Fig. 2.2: Base reduction rules of asynchronous  $\pi$ -calculus

Reduction is the method for processes in  $\pi$ -calculus to interact. If reduction is not possible, no action can be performed.

It should be noted that in  $\pi$ -calculus interactions between processes are initiated by parallel composition; with processes alone,  $\pi$ -calculus and the reduction rules are meaningless.

2.2. SESSION TYPES 17

```

P ::= \text{request } a(k) \text{ in } P

session request

| accept a(k) in P

session acceptance

|k![\tilde{e}];P

data sending

|k?(\tilde{x})| in P

data reception

| k \triangleleft l; P

label selection

|k\rhd\{l_1:P_1[\cdots]l_n:P_n\}

label branching

| \text{throw } k[k']; P

channel sending

| \operatorname{catch} k(k') \operatorname{in} P

channel reception

| if e then P else Q

conditional branch

|P|Q

parallel composition

0

inaction

|(vu)P

name/channel hiding

| \det D \text{ in } P

recursion

|X[\tilde{e}\tilde{k}]|

process variables

e ::= c

constant

|e+e'| e-e'| e \times e \mid not(e) \mid \dots

operators

D ::= X_1(\tilde{x}_1\tilde{k}_1) = P_1 and \cdots and X_n(\tilde{x}_n\tilde{k}_n) = P_n

declaration for recursion

```

Fig. 2.3: Session calculus syntax from [?]

### 2.2 Session types

A session is a predefined sequence of exchanging messages otherwise known as a protocol. Session types were developed as a typing system of the  $\pi$ -calculus for use by communication-based concurrent programming languages with basic communication constructs. The theory of session types is defined in terms of session calculus based on asynchronous  $\pi$ -calculus, originally introduced by Honda et al. [?] and their work was subsequently revised by Yoshida and Vasconcelos [?] which became the basis of session Java. Session calculus is a building block of session types, where session type defines compatible sessions in terms of session calculus.

#### 2.2.1 Syntax of session calculus

**Basic constructs** Processes exchange messages by pairs of send and receive actions. Data sending and receiving are the basic constructs in session type, along with inaction process, parallel composition of processes and name restriction ( $\nu$ ). These basic constructs can be directly translated to asynchronous  $\pi$ -calculus.

```

accept a(k) in P= request a(k) in P k![\tilde{e}]; P=k?(\tilde{x}) \text{ in } P k\lhd l; P=k\rhd\{l_1:P_1\|\cdots\|l_n:P_n\} throw k[k']; P= catch k(k') in P \mathbf{0}=\mathbf{0}

```

Fig. 2.4: Dual actions

**Label branching** Label branching is a feature in session calculus for *structured external choice*. Without label branching, it is not possible for sessions to exhibit different behaviour on different conditions or they will be incompatible. Thus the use of session calculus and session types will be very limited and only useful in serial and simple communications, if choices are not possible.

Label branching is done by sending and receiving a *label*, and based on the content of the label, the session type following the selection action can be different as long as the session type of the counterpart participant remains compatible with the receiver after sending the said label.

Session delegation Because of the name-passing property of  $\pi$ -calculus, it is possible to pass more information and use the sessions more flexibly. This allows sessions to be passed to other processes as a parameter via a channel, subprocesses can use the received session as a session rather than a value. By offloading parts of responsibilities of the parent process to the subprocesses, we can distribute processing to lower level or smaller processes, without sacrificing the advantages of using session-types because all delegated processes also follow a subset of session-type from the top level. Most importantly, the top-level process does not need to be informed about the delegation which allows a higher level view when designing distributed systems with session types.

**Duality** We mentioned the importance of interaction in the previous section (§2.1.1). A correct session type for two interacting process requires the sessions in the same channel to be 'associated with complementary behaviours' [?, Definition 5.2], this important requirement provides the theoretical basis for communication safe processes. In the syntax given in Fig. 2.3, complementary actions are shown in Fig. 2.4; these pairs of actions, when composed together, will reduce without getting stuck. A sound type system will not cause stuck errors if the implementation is correct.

As an example of session type, Example 1 is definition of a simple sum server system that adds and returns the sum of two numbers in *SumServer* supplied by *SumClient*. This will be be used in subsequent sections to demonstrate the similarities and difference between session type and its derivatives.

| G ::=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Global types                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| $\mid \ \mathtt{p} 	o \mathtt{p}' \colon \langle U  angle . G$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Message                     |

| $  \hspace{.1cm} \mathtt{p} 	o \mathtt{p}' \colon \{l_k : G_k : G$ | $\{k\}_{k \in K}$ Branching |

| $\mu \mathbf{x}.G$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Recursion                   |

| <b>X</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Type variable               |

| $\mid G$ i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Application                 |

| end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Null                        |

Fig. 2.5: Global types and type reduction from [?]

#### Example 1.

```

SumServer = accept \ a(k) \ in \ k?(\tilde{x}) \ in \ k?(\tilde{y}) \ in \ k![x+y]; \mathbf{0}

SumClient = (vk) \ request \ a(k) \ in \ k![42]; k![77]; k?(result) \ in \ \mathbf{0}

SummingSystem = (va) \ SumClient \ | \ SumServer

```

### 2.3 Multiparty session types

Session types introduced in §2.2 describes communication between two parties. When a communication involves more than two participants, the communication can be modelled by multiple binary sessions between any two of the participants. All communications between any two participants can be guaranteed compatible and error free by the safety property of binary session type. However, binary sessions cannot prevent interleaving of sessions in a communication with multiple binary sessions. Interleaving sessions might allow incorrect communication logic or cause problems such as deadlocks because the execution sequence is not determined at design time.

This will be a problem when using binary session types in a system where different participants of communication are implemented by different parties, and each party is given a protocol specification which they code according to. The final product will be correct in the local view but could be incorrect in the global view because the parties do not have the information of the global session type. Therefore to design a correct multiparty protocol, no assumption of execution order should be made and the communication of different participants should be specified explicitly.

The basic constructs of a multiparty session type are almost identical to binary session type, but add a global type (Fig. 2.5) on top of the endpoint (or local) session type. The global type specifies the global progress of the communication, and *projects* to endpoint session type for each of the participants.

Global session types provide a theoretical basis to prove that a communication is correct in the global view, where the participants and order of communication are defined explicitly in the design. The projection of global type to local type will ensure such properties are preserved after the operation.

### 2.4 Session programming with SJ

Session types are a basis for session-based programming, but do not describe a standalone programming language. As a result, session types and the object-oriented programming language Java are combined to create *Session Java* (SJ) [?, ?] <sup>1</sup>. SJ is an extension of Java and thus the syntax of SJ is identical to Java, with extra primitives for session programming. This is best illustrated with a simple example:

```

public class Server {

// Session declaration

final noalias protocol p_server {

sbegin.?(int).?(int).!<int>

public run(int port) {

final noalias SJServerSocket svr;

final noalias SJSocket sock;

try (svr) {

svr = SJServerSocketImpl.create(p_server, port);

10

try (sock) {

sock = svr.accept();

int x = sock.receiveInt(); int y = sock.receiveInt();

sock.send(x + y);

} catch ( ... ) {}

} catch ( ... ) {}

16

18

}

19

public class Client {

20

// Session declaration

21

final noalias protocol p_client {

cbegin.!<int>.!<int>.?(int)

24

public run(String host, int port) {

25

final noalias SJService svc

= SJService.create(p_client, host, port);

final noalias SJSocket sock;

try (sock) {

sock = svc.request();

31

sock.send(42); sock.send(77);

int result = sock.receiveInt();

32

} catch ( ... ) {}

33

34

}

```

Listing 2.1: SJ sum server/client

<sup>&</sup>lt;sup>1</sup>Currently, Session Java is only an implementation of *binary* session type and extension for *multiparty* session type is planned.

We now look at the *SumServer/SumClient* example again to show a basic communication system with SJ. A session calculus version was given in Example 1 in the previous section.

- 1. A client sends two numbers to the server

- 2. The server replies with the sum of the two numbers received

The communication primitives of SJ are similar to conventional socket programming (request, accept, send, receive), except for the protocol code block. The protocol defines the *session typing* of the program, introduced in the previous section (§2.2). With the session type of the program defined, it is possible to [?]:

- 1. Ensure the implementation conforms to the specified protocol by static checks at compile time.

- 2. Check that the two communicating programs are compatible, by a duality check of the protocol at the start of communication.

- 3. Simplify checking protocol correctness by abstracting away implementation details and checking only the session type.

Table 2.1 shows the relationship between protocol and Java code, which allows the communication safety checks mentioned above.

| Protocol                | SJ code                |                                  | Line |

|-------------------------|------------------------|----------------------------------|------|

| sbegin                  | accept()               | Starts a server session          | 9    |

| cbegin                  | request()              | Starts a client session          | 23   |

| ! <datatype></datatype> | send()                 | Sends an object with datatype    | 24   |

| ? (datatype)            | receive() <sup>2</sup> | Receives an object with datatype | 10   |

Table 2.1: Session type and the corresponding Java code

Below we list three scenarios in the *SumServer* example that can demonstrate the benefits of the safety checks:

The protocol is correct but the implementation does not conform to the protocol If the implementation of *SumServer* receives three integers instead of two as stated in the protocol, the SJ compiler will throw an exception.

The protocol and implementation are both correct but the protocols are not dual of each other. If SumServer replies with the result at the end of the execution, and SumClient is not receiving the final result, ie. Server: sbegin.?(int).?(int).!<int> and Client: cbegin.!<int> >.!<int>. When the connection between the two processes is established, an incompatible session exception is thrown.

<sup>&</sup>lt;sup>2</sup>receiveInt() is a shortcut to receive an int

A logic error exists in the protocol design If SumServer sends a result before receiving any values, and SumClient is also compatible with the server, ie. Server: sbegin.!<int>.?(int).?(int) and Client: cbegin.?(int).!<int>.!<int>. The same applies to analysing problems with distributed deadlocks, where the processing of the values is less important than the main source of problem - communication primitives. With SJ the developer can reason about the problem in the protocol level, eg. "Because the result is sent before the numbers are received and processed, therefore changing the arguments to SumServer do not influence the result" without necessarily understanding the operation done on the two arguments. Also because of the conformance check, we can be assured that the code implements the protocol without looking at the code to find the problem.

In session types and  $\pi$ -calculus, a new channel is 'generated' or 'restricted' by using the operator  $\nu$  channelname. In session programming, this corresponds to the action of creating a new Socket. The socket will contain transmission between the participants of communication once it is created. The send and receive object methods of the socket, and in session calculus you can only input and output on a given channel.

#### 2.4.1 Branching

When programming conditional statements, often different choices will branch to different behaviours of the program. To model that, label branching in session type is used:

| Protocol SJ code                                                                          |                                                                                                                                                                                                                          |                                                       |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| !{ LABEL <sub>0</sub> :session <sub>0</sub> , LABEL <sub>1</sub> :session <sub>1</sub> ,} | $\begin{array}{c} \texttt{sock.outbranch(LABEL_0)} \ \left\{ \begin{array}{c} \texttt{code}_0 \ \right\} \\ \texttt{sock.outbranch(LABEL_1)} \ \left\{ \begin{array}{c} \texttt{code}_1 \ \right\} \\ \dots \end{array}$ | Send LABEL <sub>0</sub> Send LABEL <sub>1</sub>       |

| ?{ LABEL <sub>0</sub> :session <sub>0</sub> , LABEL <sub>1</sub> :session <sub>1</sub> ,} | <pre>sock.inbranch { case LABEL<sub>0</sub>: { code<sub>0</sub> } case LABEL<sub>1</sub>: { code<sub>1</sub> } }</pre>                                                                                                   | Receive LABEL <sub>0</sub> Receive LABEL <sub>1</sub> |

Table 2.2: Branching in session programming

Table 2.2 shows the receiving and sending of labels. The code blocks ?{} and !{} represent receive label and send label respectively. Sending of labels is usually used in conjunction with conditional statements, for example in Listing 2.2.

```

final noalias protocol p_hwc {

cbegin.!{LOWER:?(int), UPPER:?(String)}

}

if (userInput.equalsIgnoreCase("lower")) {

sock.outbranch(LOWER) {

```

```

System.out.println("LOWER branch; Server replies with #"

+ sock.recieveInt());

| else {

| sock.outbranch(UPPER) {

| System.out.println("UPPER branch; Server replies with "

| + (String) sock.receive);

| }

| }

| else {

| sock.outbranch(UPPER) {

|

```

Listing 2.2: Example usage of label sending

#### 2.4.2 Iteration

Iteration in session programming translates to replication in  $\pi$ -calculus. In  $\pi$ -calculus processes can be repeated and this forms the loop-body of an iteration. Iteration is not part of the session calculi defined in [?] but will be formalised in this report. By using an explicit looping construct that is similar to normal Java programming (outwhile/inwhile vs. while), the reasoning of iteration is thus simpler to the programmer. Table 2.3 shows the syntax of outwhile and inwhile. The only difference between the two is outwhile controls the looping condition, and inwhile reacts passively. The iteration construct therefore also work as a synchronisation mechanism between the sessions. To implement iteration with the same semantic in MPI, the single line code might be expanded to  $^3$ :

```

// outwhile(condition)

// inwhile()

MPI.COMM_WORLD.Recv(

condition, ...);

while (condition) {

while (condition) {

4

MPI.COMM_WORLD.Barrier();

MPI.COMM_WORLD.Barrier();

/* outwhile code */

/* inwhile code */

MPI.COMM_WORLD.Send(

MPI.COMM_WORLD.Recv(

condition, ...);

condition, ...);

8

```

Listing 2.3: outwhile in MPJ Express

Listing 2.4: inwhile in MPJ Express

| Protocol                     | SJ code                                |

|------------------------------|----------------------------------------|

| ! [ session in iteration ] * | s1.outwhile(condition){ }              |

|                              | s1.outwhile(s2.inwhile; condition) { } |

| ?[ session in iteration ] *  | <pre>sock.inwhile(){ }</pre>           |

Table 2.3: Iteration in session programming

<sup>&</sup>lt;sup>3</sup>Example uses syntax of MPJ Express, a Java MPI implementation

Note that the alternate form of **outwhile** that uses **inwhile** as condition is a new SJ primitive for implementing parallel algorithm. The formalisation and proofs will be given in §4.1.

#### 2.4.3 Delegation

Sessions can be delegated to other components, to expression delegation of session in the protocol, we simply replace the type of the message by a session, as shown in Table 2.4. *delegated session* in the table represents the session type of the *initialised SJSocket* and of revdSession. If we look closely the primitives of session delegation is identical to ordinary send and receive in SJ, except the content is a session rather than a usual data type (but lends itself to the Java Object model where every type is a subtype of Object). Session delegation is an important tool to distribute tasks.

| Protocol              | SJ code                                             |                   |  |

|-----------------------|-----------------------------------------------------|-------------------|--|

| ! <session></session> | ! <session>   sock.send(delegateSJSocket)</session> |                   |  |

| ? (session)           | SJSocket session = sock.receive()                   | Receive a session |  |

Table 2.4: Session delegation in session programming

#### 2.4.4 Non session-based alternatives

The implementation of SJ is most similar to that of the MPI standard (§2.4.4) in terms of communication model (message passing) and design. There are also other distributed message passing system such as Java *Remote Method Invocation* RMI, but the design and uses are in a different domain compared to SJ.

#### Message-Passing Interface (MPI)

MPI is a message-passing library interface specification [?] and is commonly used in the high performance computing field for message-passing based parallelism.

Using MPJ Express, an implementation of the MPI standard in Java, it was shown in [?] that there are many similarities between the two but the main differences are:

**MPI has more features** SJ does not have multicast-type message send primitive, but theory for multiparty session type §2.3 have been developed for future implementation [?] in SJ.

MPI is a low level protocol which makes it prone to communication mismatch or deadlocks due to explicit message passing [?]. A communication mismatch in MPI such as a MPI\_Send without a corresponding MPI\_Recv, will not cause problem until some point in the execution. Scenario 2 of safety check examples above will will cause MPI but not with SJ. In a distributed database system,

2.5. AXEL 25

it would require a rollback on all previous calculations. SJ's safety properties (§2.4) will prevent the incompatible sessions from starting.

**SJ** has high level session abstraction so the code is more structured and more readable than MPI, this gives the programmer an advantage to focus on more important communication/protocol details.

**SJ** is not an external library SJ was designed to be a full object-oriented programming language. Implementations of MPI are external libraries since it is only a communications standard. As a domain-specific language, syntax for tasks common to communications programming can be built into the syntax and will be more natural to use, despite the small difference between Java and SJ. Examples include the try-channel syntax to catch exceptions from within a specific channel (line 8 in Listing 2.1), and the different forms of **outwhile/inwhile** as a session-type specific looping technique.

Taking the example of outwhile and inwhile in Listing 2.3 and 2.4 again, the iteration feature in MPI is less readable than in SJ because the special iteration syntax is not found in MPI.

#### 2.4.5 Related work

Implementation of session types had been developed for other languages such as Haskell [?, ?]. Other work on session-type with C-like languages [?, ?] does not take the direction of implementing the full session type system. SJ is the first practical session-type based object-oriented programming language.

#### **2.5** Axel

Axel [?] is a heterogeneous computer cluster built at Imperial College. The cluster consists of 18 computing nodes, and each of the nodes contains a x86 CPU, a number of *Graphics Processing Units* (GPU) and most of the nodes contain a *Field Programmable Gate Array* (FPGA) device. FPGAs and GPUs are used on Axel as hardware accelerating components.

Axel is the target platform for this project. We wish to deploy SJ on the cluster and use session programming to improve parallel design. Below is an overview of hardware and software currently on the cluster.

#### 2.5.1 Hardware arrangement

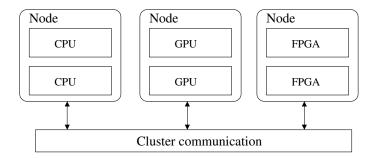

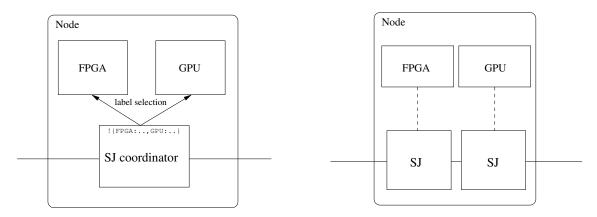

**NNUS clusters and UNNS clusters** There are two ways of grouping hardware accelerators (or *Processing Elements*, PE) in a heterogeneous cluster, namely *Nonuniform Node Uniform Systems* (NNUS) and *Uniform Node Nonuniform Systems* (UNNS).

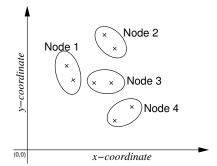

Fig. 2.6: Nodes in a generic UNNS cluster

In a UUNS cluster, each node of the cluster hosts a single type of PEs. In the example of Fig. 2.6, three nodes of the cluster hosts CPUs, GPUs and FPGAs respectively. For nodes that hosts non-CPU PEs, special hardware are needed to control the nodes because they cannot run ordinary operating systems. Examples of UUNS clusters are SRC-7 MapStation and RASC server from SGI [?].

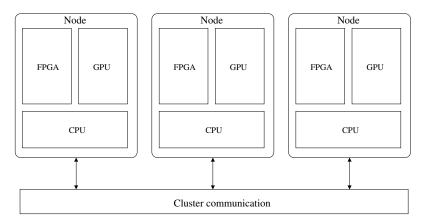

Fig. 2.7: Nodes in a generic NNUS cluster

On the other hand, in a NNUS cluster, each node of the cluster contains different PEs (thus *Nonuniform Node*). The PEs of the NNUS cluster example in Fig. 2.7 shown to be on the same node are CPU, FPGA and GPU. All nodes in the cluster have the same arrangement. This makes it easy to put together commodity hardware and build a cluster (eg. Beowulf clusters)

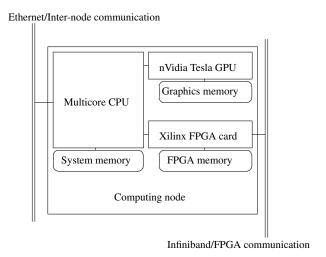

Axel is a NNUS heterogeneous cluster, meaning that each node in the cluster will contain different types of PEs. Each node on Axel can be used as an independent x86 PC equipped with hardware accelerators (FPGA board and GPUs). The details are shown in Fig. 2.8.

#### 2.5.2 Software

All the nodes in the cluster run a standard Ubuntu Linux (amd64 architecture). The following software and frameworks are installed to program different hardware components of Axel:

Fig. 2.8: Axel's NNUS arrangement

**CPU** The CPUs are standard multicore x86 CPUs and GCC is used with OpenMPI<sup>4</sup> to produce executables to run on the CPU. The main use of the CPU in a complete Axel application is to coordinate communication between computing nodes using MPI, but it can also be used for general CPU based computation.

**nVidia GPU** All the GPU used are nVidia Tesla cards, designed for high performance computing rather than general graphics rendering. nVidia provides the *Common Unified Device Architecture* (CUDA) framework for GPU programing. CUDA is is the standard *General-Purpose computing on Graphics Processing Unit* (GPGPU) framework for nVidia products and provides a C-like environment for the Tesla GPU platform [?].

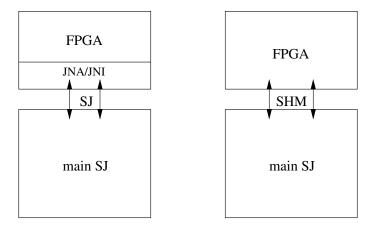

**FPGA** Xilinx ISE 10.1 is used for development of hardware logic for FPGA hardware compilation to the FPGA devices, and all the runtime access to the FPGA devices are done in a very low-level memory mapped I/O and DMA, via a vendor supplied library, exposing an API in a C programming environment.

The compilation and execution of an Axel application is not done in a single executable. The application consists of a CPU-part that initialises the data and distributes to the GPU-part and the FPGA-part of the application. The workload split is described in an XML file for maximum flexibility, which is first read by the CPU-part to segment the data. It is possible to setup the application such that the CPU will do part of the calculation but it is usually used exclusively for I/O coordination and inter-component/inter-node communication. A **map-reduce** framework is used in the cluster for parallel programming where segments of calculations are 'mapped' to the computing elements (eg. FPGA, GPU cores) and the results are 'reduced' and collected by the I/O handling code running on the CPU which, in turn, 'reduces' the results to the master node which started off 'mapping' the input on each computing node.

<sup>&</sup>lt;sup>4</sup>An implementation of MPI in C, see §2.4.4 for details of MPI

#### 2.5.3 Performance

CPUs are designed for general purpose computation, and because of the underlying von Neuman architecture, the CPU works like an instruction interpreter and follows a fetch-decode-execute cycle to execute stored instructions. It is thus very flexible, but sacrifices the performance in a computation heavy program, where most of the execution time was spent on fetch and decode instead of the more important execute step.

Until recently, GPUs are used solely as graphics rendering hardware. With the increasing demand of modern gaming software and high throughput graphics calculations on display cards, the graphics manufacturers moved from using fixed numbers of dedicated vertex and pixel shaders to unified shaders. This allows a dynamic allocation of graphics hardware for different purposes and higher utilisation of the graphics hardware. GPU becoming less specific to graphics processing gave rise to GPGPU, where GPUs can be used for non-graphics calculations in a limited way. The advantage of GPGPU is the number of graphics processing **cores** available. These cores can do only a small number of tasks at one time but with multiple cores processing is done in parallel. Typical gaming GPUs come with a few hundred processing cores.

FPGAs essentially allow hardware execution of computer programs. As there is no need to interpret or decode the program code and can be executed directly in hardware, compared to the interpreted code model of CPU, there is less wastage of resources. Most important of all, FPGA can be easily reconfigured to carry other tasks unlike immutable dedicated hardware accelerators.

With the reasons stated above, GPUs and FPGAs are much more suited to the use cases of parallel high performance computing. Results of benchmarks [?] showed that utilising all the components gives a much better performance than using the components individually, where the magnitude of acceleration is in the descending order of FPGA, GPU and CPU.

On the GPU-only version and the multithreaded CPU version, the execution time of an n-body simulation of 81902 particles in a single time step is 1.1 times and 3.5 times slower than 10-core FPGA version respectively. In the heterogeneous version which uses both GPU and FPGA in a processing node, the workload is load balanced by assigning 2/3 of workload to FPGA and 1/3 to GPU, this gives the overall speedup of 2.1 times over the FPGA-only version.

### 2.6 Parallel Algorithms

#### 2.6.1 N-body simulation

N-Body simulations are systems to simulate particle movement and interaction due to gravitational forces action on each other.

Each particle in the n-body simulation has a position, vector velocity and mass. In each time step, the positions and velocity of the vectors are recalculated using the velocity and acceleration. The base algorithm is shown in the algorithm below (from [?]).

```

for (i = 0; i < N; i++) {

for (j = 0; j < N; j++) {

```

```

if (j != i) {

rx = p[j].x - p[i].x;

4

ry = p[j].y - p[i].y;

5

6

rz = p[j].z - p[i].z;

dd = rx*rx + ry*ry + rz*rz + EPS;

8

d = 1 / sqrtf(dd * dd * dd);

9

10

s = p[j].m * d;

11

a[i].x += rx * s;

13

a[i].y += ry * s;

14

a[i].z += rz * s;

15

}

16

17

}

```

Listing 2.5: An algorithm for n-body simulation

N-body algorithm is highly parallelisable because every particle in the algorithm does not interfere with the content of other particles during the calculation in a time step. The calculation for each article can be done individually in parallel by different computing components.

**Current Implementation on Axel** On Axel, the implementation is a straightforward translation of the algorithm, by looping over each particles. The i-loop is split evenly to different nodes and the j-loop is partitioned for FPGA and GPU to compute. The results are then distributed using the MPI\_AllToAll function to other nodes.

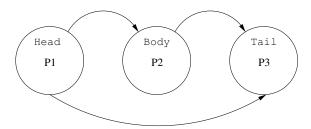

Implementation in SJ In SJ, due to the lack of a multicast-type send, the algorithm cannot be implemented directly. Instead, the n-body algorithm is implemented in 3 parts using a ring topology [?]. The Master process forwards initial data to a number of Worker processes, which is chained together and the last Worker process connects to the Master process to complete the ring. Since the session type of the first and last worker that communicates directly to the Master process, the last Worker is slightly different from other Workers, we need to further distinguish them from other worker components. The Worker processes will carry out most of the computation.

In each iteration the data is forwarded to each Worker through the chain, and adds the results of previous iteration to the data set to be forwarded to the next Worker and continues until all nodes have received set of particles from other nodes once. When the data is seen by all Workers, the positions of each particles are updated using the overall velocities and acceleration acting on each particles.

### 2.7 Summary

In this chapter we have introduced a theoretical framework for modelling structured communications in concurrent systems. Session calculus, a process calculi based on the asynchronous  $\pi$ -calculus and its typing system - session types, forms the basis of a session programming. Session typing ensures that only compatible processes can establish a session and guarantees communication safety.

We then described a full implementation of session-based programming language *Session Java* (SJ), combining Java with sessions.

Next we detailed the target platform for our project, Axel, a cluster with FPGAs and GPUs as acceleration hardware. We also included a comparison of performance between the different components in existing implementations to see a general picture.

Finally, we finished the backgrounds by looking at the differences in parallel programming model of the existing n-body algorithm implemented in Axel and SJ.

## Chapter 3

## **Design and Implementation**

In this chapter we will first look at an overall design of parallel applications with SJ on Axel (§3.2), then an implementation of the n-body simulation with SJ on the Axel cluster using CPU and FPGA (§3.3).

Next, we will present a translation of our n-body implementation in SJ to C (§3.4). We will detail the main contribution of the translation, a SJ communication primitives library for C (§3.4.2). The C translation brings session typed SJ programs to C, which is a much more suitable target language and programming environment for high performance computing.

### 3.1 Design goals

The aim of the project is to develop an approach for designing parallel high performance applications on heterogeneous clusters with session programming. The main criteria we considered were:

**Efficiency** Existing implementations of parallel algorithms on heterogeneous clusters are very efficient. We aim to keep the performance of our designs as close to current implementations as possible, while getting the advantages of session programming.

(Communication) Safety Session types were designed such that a communication between incompatible sessions will not begin and programs will behave according to its predefined protocol. It is difficult to verify correctness of complex parallel applications design, but session types and their safety property can guarantee the programs are free from incompatible interaction patterns.

**Readability** Session programming is a high level description of communication. Existing parallel design processes on clusters typically involves using low level libraries and working close to the metal. The instructions to develop for these libraries are verbose and require very explicit instructions (eg. MPI, §2.4.4) for simple tasks, which obfuscates the more important details of process communication. In contrast, the high level SJ abstracts most

of the implementation in the runtime system such as the transport medium (TCP vs. UDP vs. shared memory) and puts the focus on communication. Design errors can be identified easily with help of session typing §2.2 and automatic type-checking with SJ §2.4.

However, readability in session programming is a property that comes from structured code and the high level of abstraction and cannot be easily quantified by numerical metrics.

Before we commence our discussion on design and implementation of SJ applications on Axel, we should point out that Axel is an example of NNUS cluster (§2.5.1 contains details of two kinds of cluster arrangement). While our design is targeted to Axel specifically, in theory the design principals can be generalised and applied to NNUS clusters with similar architecture.

#### 3.2 Session Java on Axel

In this section we will discuss the design and the overall architecture for SJ applications to run on Axel.

#### 3.2.1 Overall design

Session Java is an extension of Java. Features of object oriented programming are available in SJ and allow us to create structured and easily reusable code.

The main processing elements on the Axel cluster are CPUs, GPUs and FPGAs. In the initial phase of development, we first implement our choice of algorithm in pure SJ. This allow us to identify any problems with the communication design before involvement of the new hardware, and familiarise with the facilities available on Axel.

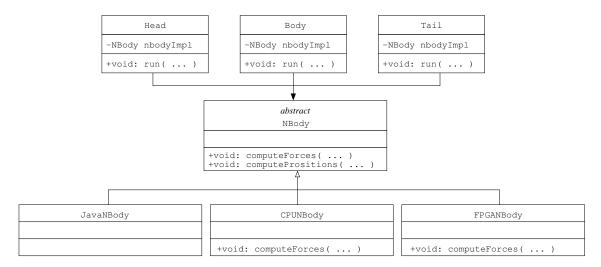

#### **Class organisation**

By organising classes into suitable packages and class hierarchy, we reduced the efforts needed when implementing for FPGAs or any other acceleration hardware. This is possible because acceleration hardware do not participate in the flow-control of the algorithms. Typically complicated and computation heavy sections of an algorithm are isolated to a single function. The function will then be implemented on acceleration hardware, and no changes to the other parts of the program are required.

**FPGA:** do one thing and do it well It is uncommon to delegate multiple tasks during a single execution on one piece of acceleration hardware. Suppose two different tasks are implemented on the same piece of hardware, and the two tasks are executed in parallel. Tasks and programs are mapped to the physical hardware on FPGAs. When #1 of the two tasks are being executed, only a portion of the hardware is used - the rest of the hardware will be idle because they are designed to run task #2. Therefore we are not fully utilising the hardware every time the hardware is used.

Fig. 3.1: Simplified UML diagram of our system

Despite FPGAs are known for the ability to reconfigure at runtime, it is a lengthy process and offers no practical advantage if we need to switch between tasks and reconfigure constantly.

In the class diagram shown above, NBody class can be replaced by the main component of other algorithms. This will allow different algorithm to use the same class structure for their implementation, such as an implementation of inner product we will detail in next chapter in §5.2.

**NBody** The abstract class contains all functions used by the algorithm. This class should be replaced by a similar class that contains all core functionalities when implementing other algorithms.

**JavanBody, CPUnBody, FPGANBody** These classes are solid implementations of the NBody class. The main functions will take the input values and map them on different hardware or software implementations, then return the results as a Java array. The process is transparent to the caller.

**Head, Body, Tail** classes contain code to set up the topology of the application and SJ communication between nodes of the cluster.

Head is the component that runs on the first node and act as the initiator.

Body is the worker component and can be chained together with other Body nodes.

Tail is the last worker component that connects Body with Head on the other side of the ring. More details on the sessions of the components will be given in the next subsection. §3.2.2

All of the classes take a constructor of class NBody to select the implementation to use. This allows combinations such as FPGANBody/Head, CPUNBody/Body or JavaNBody/Tail to be constructed flexibly and easily.

This design uses the well-known design patterns of *strategy* and *template method* [?]. The two patterns help separating communication from the algorithm body, and make it easier to reuse

```

public abstract class NBody {

public abstract void computeForces( ... );

}

4

public class JavaNBody extends NBody {

public void computeForces( ... ) { ... }

7

8

9

}

10

public class Head {

11

NBody nbody; // set by constructor or injected

public void algorithmBody( ... ) {

14

nbody.computeForces( ... );

15

16

}

}

18

```

Listing 3.1: Strategy/template method pattern

the same algorithm outline and implement it in different hardware. Listing 3.1 outlines how the classes are used.

#### 3.2.2 Application topology and session typing

The implementation of a n-body simulation follows a similar ring topology as described in §2.6.1, the only difference is the addition of initial hardware set-up and tear-down phases at the end of execution.

#### **Session interaction**

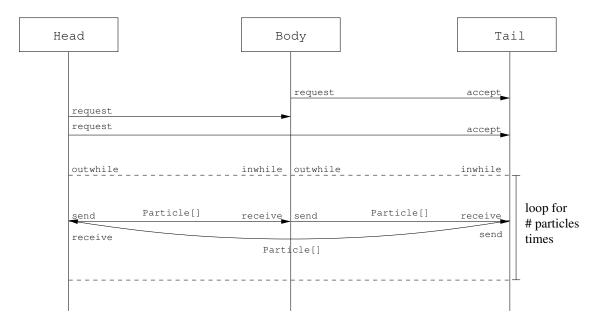

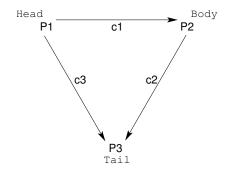

The structure we are going to describe is not limited to n-body simulations and can be adapted to any algorithm that uses a ring topology. Fig. 3.2 shows the interaction between the node and Table 3.1 gives the session declaration in each of the nodes.

We have covered the meanings of components of SJ protocols in §2.4, and we will revisit the declaration shown here in the next chapter (§4.7.1).

#### Partitioning of data

The input data is uniformly partitioned into n parts, where n is the number of cluster nodes in the simulation at execution time. Each node is responsible for outputting the particle positions of its allocated set of particles, and will keep track of their velocities and acceleration components at each steps of calculation.

Fig. 3.2: Interaction between Head, Tail and a single Body node

| Node                                     | Session between     |        | SJ session declaration (protocol)            |  |

|------------------------------------------|---------------------|--------|----------------------------------------------|--|

| Head                                     |                     |        | cbegin.![?(Particle[])]*                     |  |

| Head                                     |                     |        | cbegin.?(int)![! <particle[]>]*</particle[]> |  |

| $oxed{ Body Body}_{i-1} oxed{ Body}_{i}$ |                     | Body i | sbegin.! <int>.?[?(Particle[])]*</int>       |  |

| Body                                     | Body $i$ Body $i+1$ |        | cbegin.?(int).![![Particle[]]]*              |  |

| Tail Body Tail                           |                     | Tail   | sbegin.! <int>.?[?(Particle[])]*</int>       |  |

| Tail                                     | Tail Head Tail      |        | sbegin.?[! <particle[]>]*</particle[]>       |  |

Table 3.1: SJ session declaration for ring topology

The numbers in Fig. 3.3 represent the node number which the particles are from. In the *initial* round, velocities and acceleration components of each particle are calculated against each other in the same node.

Next, each node forwards the initial set (or the received set after the initial round) of particle positions to the adjacent node. Since velocities and acceleration components can be accumulated, when a set of particles is received, each node can immediately update the velocities and acceleration of their **own** set of particles without keeping a copy of the received particles.

After 3 rounds, all nodes will have seen all the particles and can perform calculations to update the positions of the particles they were allocated. With n nodes participating in the simulation, the calculate-and-forward step is repeated for n-1 steps instead of 3 in our example above in order for all nodes to see all particles at once.

| Node/partition # | Initial | Round 1 | Round 2 | Round 3   |

|------------------|---------|---------|---------|-----------|

| Node 1 (Head)    | {1}     | {1,4}   | {1,4,3} | {1,4,3,2} |

| Node 2 (Body)    | {2}     | {2,1}   | {2,1,4} | {2,1,4,3} |

| Node 3 (Body)    | {3}     | {3,2}   | {3,2,1} | {3,2,1,4} |

| Node 4 (Tail)    | {4}     | {4,3}   | {4,3,2} | {4,3,2,1} |

Fig. 3.3: Partitioning of data and calculation for 4 nodes

#### 3.3 S.J with FPGA

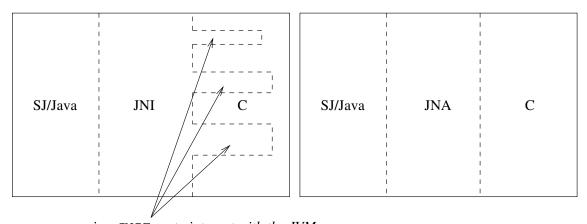

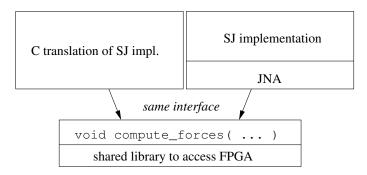

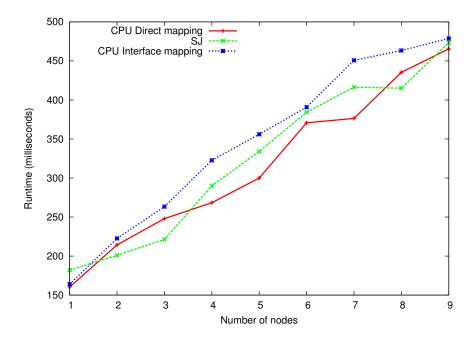

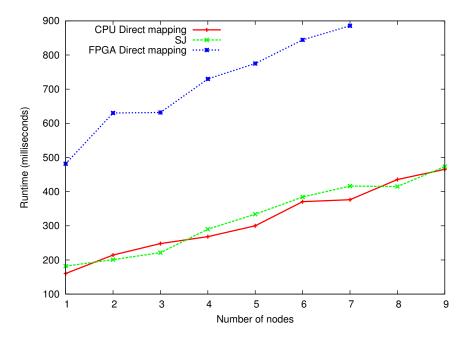

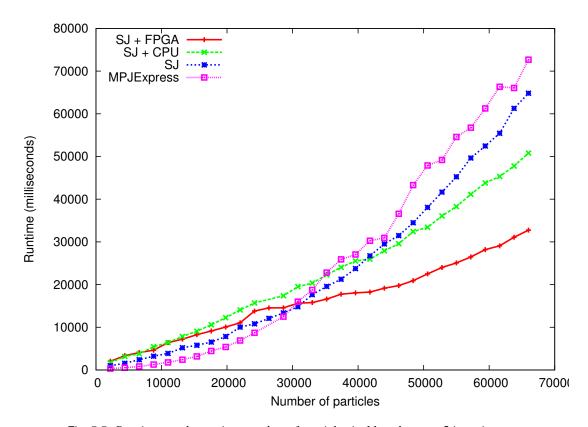

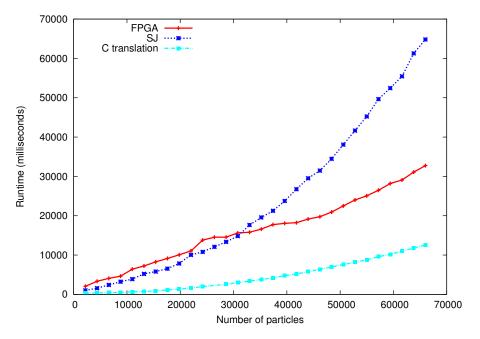

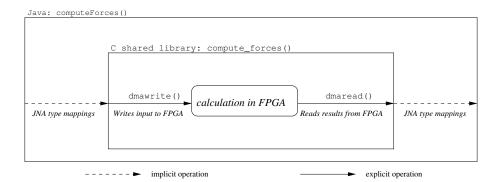

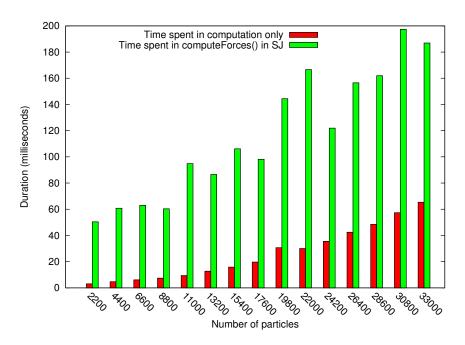

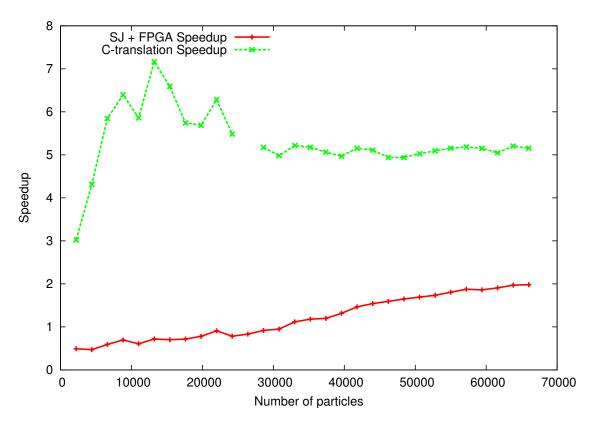

After looking at the general architecture of SJ parallel applications on Axel, in this section we will detail an implementation of the n-body simulation using FPGA.